V-FET・妙なコンプリメンタリPP

20110908〜20120624

目次

昔話ですが 1980年代・・・

ネルソン・パス氏の「真剣なお遊び」から

妙なコンプリメンタリPPへ 20110911〜

OPT併用を思いつく 20110913〜

イケそうなので欲張ってみます 20111009〜

前段はSRPP 20111010〜

プチ難題(1) 20111030〜

また開放構造? 20111120〜

プチ難題(2) 20120121〜

完成間近だが 20120505〜

プチ難題(3) 20120521〜

とにかく先へと 20120526〜

プチ難題(4) 20120603〜

最終回路・特性 20120616〜

まとめ 201206**〜

地元発表会に出品 20141109

はじめに

今なら「SIT」と呼ぶべきかもしれませんが、本件の2SJ18/2SK60も2SK79も「SONYのV-FET」です。以後「V-FET」と勝手に呼称します。

なお、「妙な」は・・・おいおい述べてまいります。

昔話ですが

1980年代・・・

中途半端な昔話です。V-FETの“短い旬”は過ぎて、市場からも消えたかと思ってた頃、当地JUNK店にペア性が怪しいJ18/K60組が出てました。

妙な能書きやら酷評は気にはしてました。バイアスに絡む厄介さを感じ、手掛ける事も無かろう・・・と忘れてた素子ですが、「これは最後の機会か?」とばかり衝動買いしてしまいました。その後もなぜか「未だに売ってる」不思議なデバイス。

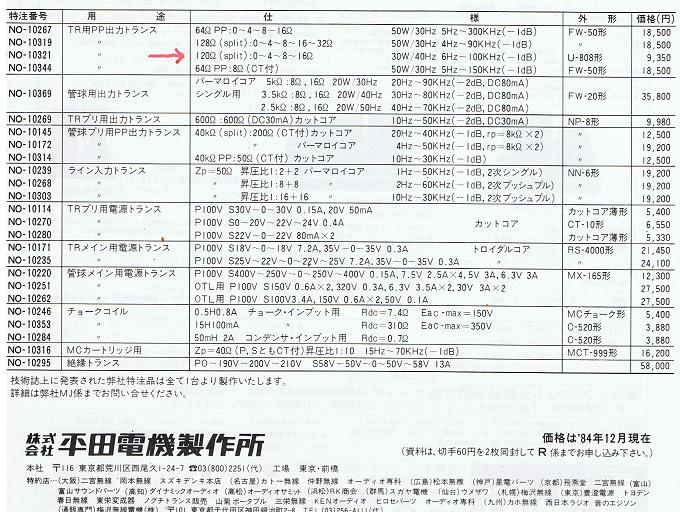

初期構想では、TANGO特注OPT・No-10321と組むつもりでした。これはMJ誌1984/4月号の新井晃氏の記事で紹介され、MOS-FETの並列給電SEPP用に作られたもの・・・と思います。

初期構想では、TANGO特注OPT・No-10321と組むつもりでした。これはMJ誌1984/4月号の新井晃氏の記事で紹介され、MOS-FETの並列給電SEPP用に作られたもの・・・と思います。

この旧タンゴ・平田電機の広告には、新井氏のほか、武末先生や森川忠勇氏、石井義治氏などの寄稿家による「特注No-」シリーズが掲載されています。画像sizeの都合で上半分を省略しましたが、FG-50S・FG-20-64S・CH‐200m-1.5・PB-20S・・・一時的に標準?化されたMOSアンプ向きMODELが写真付きで紹介、楽しくもヘンな時代でした。

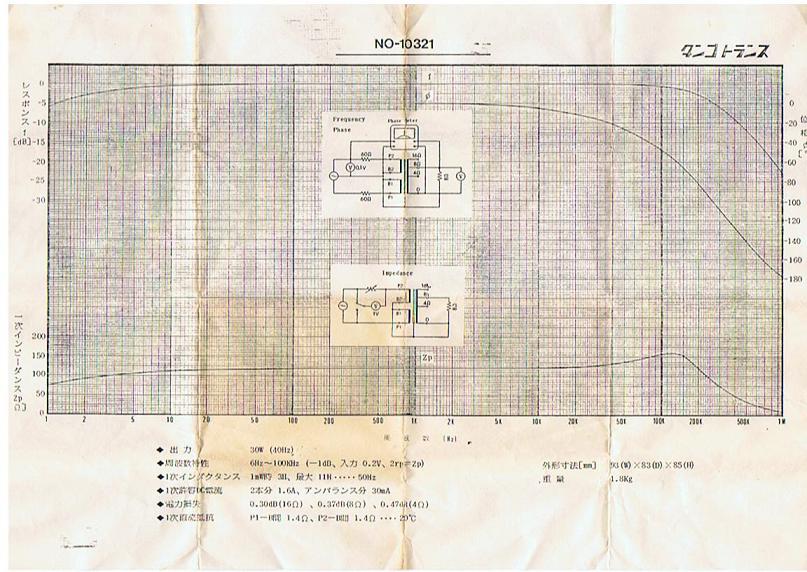

No-10321に添付の図は標準PP測定例の特性ですが、並列給電...ではどちらかの巻線はP端子が接地電位に変わりますから、高域特性も変わるだろうなと想像します。

No-10321に添付の図は標準PP測定例の特性ですが、並列給電...ではどちらかの巻線はP端子が接地電位に変わりますから、高域特性も変わるだろうなと想像します。

結果の先走りですが、出力段込みのF特を見る限り添付図の高域特性は維持されてて、さすがTANGOさん・・・と。ただし、他社の競合製品など無いので、比較対象のない「印象」のハナシ。

V-FETでもやれるさ・・・などと、見聞きしてた「厄介さ」は脇において、なんちゅう安易な(ムーディーな)発想かと赤面の至りでもあります。

案の定、電源・バイアス関連が詰めきれず、実験もしないまま放置ネタに。

2SK79は若松通商で購入・・・首都圏在住時だが、購入動機が思い出せません。

本件に絡める気でいたんだろうか。

3行空けのために・・・こげなことを

その後、「初めてのトランジスタアンプ」での半導体いぢりを経て、2006年には通常の±電源・ソースフォロワSEPPでプチ実験をしました。承知のはずの「厄介さ」を身をもって実体験、再び放置に至ります。

詳細は省きますが、中途半端な電源電圧では所定のアイドリング電流(以後Idと)の2〜3倍流れる領域が見つかります。アプローチが変なのかもしれませんが、電源ONの短い瞬間だろう事象でも気になりました。

4袋のペア?サンプルの一組で、

2SK60:Vds=15V、Id=100mA、Vgs≒−11.5V。

2SJ18:Vds=−15V、Id=100mA、Vgs≒14.9V?・・・

コレ見て、他の3袋を調べる気が失せた・・・。

後にこれらは、μが低い方の端っこランクと知る。

ネルソン・パス氏の「真剣なお遊び」から

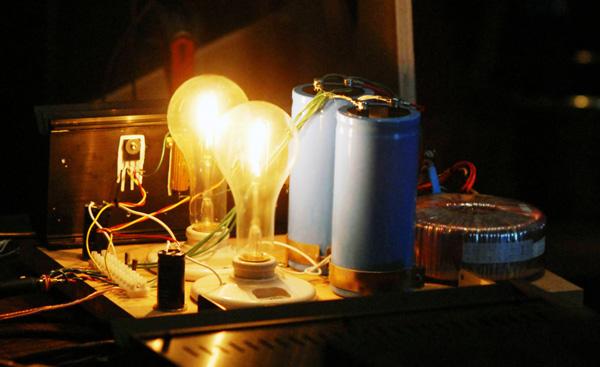

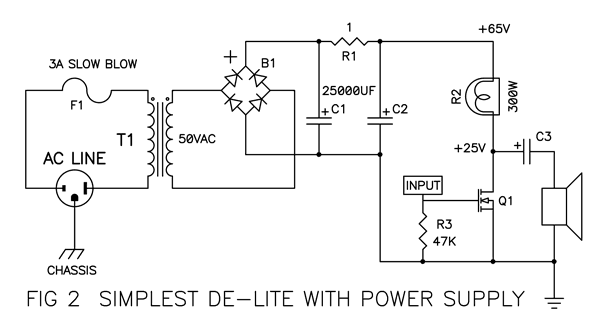

新たなきっかけは唐突に訪れました。ラ技2011/9月号の「DE-LITE AMPの製作:ネルソン・パス」です。30MP27・OTLを手掛けて既に2年・・・之奴をほっといてまでして、道草に迷い込んだ次第です。

パス氏の作品は「デプレッションモードFET、A級シングルエンデッド、無帰還、カレントソース出力」アンプです。同時に連想したのは故藤井秀夫氏の管球OTLシングルアンプでした。無駄を承知で出力管の電流経路に少なからぬ抵抗を挿入し、容量結合で8Ω負荷に小出力を取り出す理屈は共通しています。これをみて「真剣なお遊び」精神をお持ちの方と理解しました。

http://www.diyaudio.com/forums/diyaudio-com-articles/160464-de-lite-amplifier.htmlからの引用です。

ラ技1994年10月号の藤井秀夫氏による「6C33CパラシングルOTLアンプの製作」。

パス氏のは電球負荷ですが、藤井氏はMOS素子の能動負荷です。まあ・・・藤井氏は後に固定抵抗負荷Ver.も発表されてますので、“好み”が伺われるトコロではあります。

3行空けのために・・・こげなことを

単純に2SK60に置き換えただけのアンプを拵えようかと考えましたが、電球ではON直後の抵抗値が低すぎる。V-FETでやるならばフツーの固定抵抗の方が安全だと思うし、例の厄介なバイアス関係がアタマを悩ませる・・・などと考えてて

3行空けのために・・・こげなことを

妙なコンプリメンタリPPへ

20110911〜

抵抗負荷をV-FETのソース側に置き、自己バイアス兼用にすりゃ安全に起動できそうだと考えたのです。端っこランクの深いバイアス電圧が、頃合(最適とは言えんが)の動作点に落ち着く要因に?。

更に次の瞬間!・・・せっかくコンプリ素子(ペア性は?だが)があるんだから、逆極性のシングル2組の出力を“合成したら?”と。

テキトーなPTで±電源を拵え、それぞれのソースフォロワ2組を並べた実験です入力は共通ですが、出力は独立。

その個別出力波形を調べますと、イケそうな感触です。

情け無い話だが、波形観測はしたものの、撮影・記録を失念・・・。

DCカットのコンデンサを介して両出力を短絡しますと、信号振幅は変わらず、リプルハムと揺らぎは減りました。負荷の2.2kΩに深い意味は無く、テキトーな充電経路程度のつもり。

イケると確信しました。

情け無い話だが、波形観測はしたものの、再び撮影・記録を失念・・・。

実験基板下のPTは20W+20W級セットのJUNKモノ。あわよくば、最終作品に使えんものかと目論んで、その按配探りも。

10行空けのために・・・こげなことを

振幅を上げると更にクロスオーバー歪み、深いAB級PPを自己バイアスでやってるようなもの。

ソース抵抗値のADJ・・・バイアスを浅くしまして、まあまあ改善。

この時のIdo≒0.3Aでして、Pd≒4W。チャチな放熱器では、そろそろ気になる発熱です。

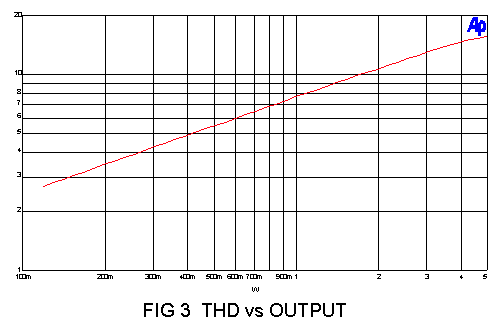

上記動作点での歪み率特性です。まあ・・・実用レベル、音が聞けなくは無い程度には。

これだけだと解り辛いのですが、2W辺りで既にクロスオーバー歪が見えました。音が聞けるのであって、良好かどうかは・・・聞いておりません。

V-FETが「生きている」事にもいささか感動してます。“生存”が怪しげだった古いタマが、マトモに動作して安堵したのと同じ感覚でした。

OPT併用を思いつく

20110913〜

「生きててくれりゃ、それでイイ」・・・と考えるだけではつまンない。Pdmax=63Wのデバイスとしては、まあちっと仕事をしてほしいとイロケが出てきます。ソース抵抗が回路の消費電力の半分食ってるのは・・・DE-LITE AMPと同列でしょう。ヘンテコでもPP動作なのだからと、効率が気になってます。

ソース側に負荷を与えるのは必須事項ではありません。「DE-LITE AMP」も「6C33C-B・OTLシングル」ドレイン/プレート出力です。V-FETの「厄介さ」はバイアスの煩わしさですので、手始めに「素子を飛ばす」事故の無いよう、自己バイアス兼用負荷を試みた次第です。

前振りしといた平田電機TANGOのNo-10321出力トランスが活かせそうです。

並列型SEPP用の、1次2巻線分離構造なので可能な回路。バイアス給電方法と、ソース抵抗値の選定に悩みます。

絵ヅラがどうあれ・・・これは標準PPそのものと変わりませんね。AB級動作は成立するし、OPTの磁気結合による・・・挙動は並列PPそのものです。念のため。

バイアス回路に悩み抜いて、まずこの回路。まだスライダックで起動しないと怖い段階です。

ハムが多く、ケミコン増量など安易なアプローチ中。DCバランスを故意に崩すとハム低減(2mV→0.63mV)など不可解な事態も。

浅いバイアスが試せるが、Pdo増大のため放熱器の強化(同じのを2枚張り合わせ)しました。

荒っぽい管球pp風にはなりました。デバイスのペア性がアレですし、ACバランスも加減しようが無いのに、まあまあかなと。Ido≒0.45Aは熱的上限と思う。

3行空けのために・・・こげなことを

イケそうなので欲張ってみます

20111009〜

AC18V巻線からの約±22Vで実験を進めておりましたが、8Wほどの出力です。またまたPd=63Wデバイスの仕事をして欲しくなり、同じPTの2個使用で±45V動作へと強化しました。放熱器との兼ね合いでIdoは絞ります。

同時に、バイアス電源を「半」分離しました。出力段電源のハム(リプル)対策用の抵抗も絡み、ON時のタイミングが調整?できます。Idピークの緩和が目的です。

Ido≒0.1A時の電圧関係を記入しました。OPT付きとはいえ、DC電源ラインに固定抵抗を挿入するのは「それなり」の損失を覚悟せねばなりませんが、コレの塩梅でON直後のIdピーク値が変わります。同時にリプルフィルターとして効きますので、最大出力が20W台を維持できる抵抗値を探りました。

スッタモンダの末、概ね緩和できたIdピーク。N/Pchとも0.25A程。欲張った初期はこれが1A超でした。Idmax=5Aと書いてあるデバイスですが、気になって。

注:20120211時点で撮り直し写真。20111010頃の状況を再現させた「つもり」なんですが、胡散臭いのはごもっとも・・・。

良くは無いが「まあまあ」の特性で20W超得られるようになりました。でも・・・シングルアンプみたい。

Ido>0.2Aではやっぱり熱い。参考データですが、A級領域を拡大しても大して良くならぬ・・・0.1Aで決まりです。

訂正あり:OPT2次8Ωタップ16Ωタップに8Ω負荷・・・、RLpp=60Ω相当動作です。

放熱器は「V-FET_6実験中」同様の片面フラットx2の張り合わせ。意匠の目論見もあって、これを最終的にも使いたい。しかし10Wも食わせられんサイズでもあり、痛し痒し。

2行空けのために・・・こげなことを

←この辺の・・・

後日、出力段用電源の、整流→平滑10000μF間に挿入した「つもり」の2.2Ωが、迂回しとッたチョンボに気付く・・・。修正してON直後のIdピークは更に減少したが、電源電圧の低下も招く。パワーサーミスタの使用を検討。

前段はSRPP

20111010〜

J18/K60の出力段だけでも、そこそこの音は鳴る利得(+1.2db)ですが、冒頭で触れた「2SK79」を絡めます。「全段V-FET」と呼べるし、多分ヨソで使うネタもないし・・・随分単純な理由です。おっと、若干の負帰還も掛けたいのです。ソース接地2段アンプなのでメンドーは無いかと。

若松の2SK79ペアにはご丁寧にも、SRPP用途想定の概略メモ添付。使用例・定数値まで書いてありました。なお、SRPPはタマ・FET共に初めてです。雰囲気で決めました。最初は安易に若松推奨定数を、Nch出力段の元電源+45Vで試しました。ところがSRPP段の負荷が22kパラと重く(後に改善)、10Vrms(12.5W/8Ω)時で波形が歪みます。ドライブし切れてない印象。

次も安易ですが、SRPP段の供給電圧増強を考えました。使用PTには細々とした遊休巻線があり、2個分6巻線を総動員しますとAC68Vが得られました。ブリッジで≒100Vが期待できます。

ケミコン耐圧が危ないまま、強行。各ソース抵抗も同一にしたけど、上下Vd揃わず・・・これも強行。整流直後の80V台は、意外だったが・・・強行。

ケミコン耐圧が危ないまま、強行。各ソース抵抗も同一にしたけど、上下Vd揃わず・・・これも強行。整流直後の80V台は、意外だったが・・・強行。

SRPPと出力段、両者組んでの歪み率数値が定まりません。2W付近で0.1〜0.5%の変動すら見える事があります。周期性は無きに等しく、ゆ〜ったりと不規則に、時にはやや速く変動します。0.1W以下の低レベルの方が落ち着いている印象もあり、しばしば経験する電灯線電圧変動由来の「揺らぎ」とは趣が違います。実際にVP-7720Aの400Hz・HPFは、全く・・・と言うほどに効きません。

SRPPに特別の思い入れはありません。音がど〜たら・・・の意見もありませんが、毛嫌いするほどでもなく“遊び半分”くらいの意味で採用しました。フツーの抵抗負荷ソース接地一段でもカマワンと思います。その態度からでしょうが、ロクな単体データを記録しておりません。悪しからず。

プチ難題(1)

20111030〜

SRPPと出力段の間で、“中途半端”な2次歪の打ち消しが行われているとは感じておりますが、どうやらその塩梅が一定しないと推定します。では、なぜ?。

実は、OPT使用の実験途中から出力部のIdoは、電灯線電圧変動に影響を受けている事が解ってはいました。それは「負」の依存性なので、安全側だと安易に放置していたのです。どうもそれが今頃クローズアップされてきたようです。

もう少しクドく考察すれば、N/PchのデバイスのPP平衡性の崩れかと感じます。電源電圧の変動に伴うIdoの変動は・・・N/Pchで一致しておりません。元々ペア性の怪しい組なので、少なからぬ2次歪が残留しておりますが、SRPP前段との打消しが安定するには、両方の2次歪が安定しなければなりません。SRPP側も非安定電源ですので、幾らかの影響は想像できますが、PPの平衡崩れの方が、より強く影響を受けたケース、と感じます。

いっそ前段を完全無歪みにすれば、出力段の歪が打ち消され無いまま出るので、ある程度安定した歪み数値に落ち着くと思います。逆に、SRPPで大歪みを発生させ、これが殆ど打ち消しきれぬ歪みのまま出力させる?・・・どちらも大変でしょうし、後者はおかしいよね。

無策・・・・これは20111010時の実験回路で試した、抵抗でバイアス電圧を与えた時です。

無策・・・・これは20111010時の実験回路で試した、抵抗でバイアス電圧を与えた時です。

改めて調べますと、これは酷い。安全側ではあるものの、放置できない動作状態と言えます。N/Pch間が完璧に一致して、歪み率変動が見られなかったら、見過ごしてしまったかもしれませんが。

最終的な歪み率に「大して」関わらないかもしれませんが、Idoの電源電圧依存性をナントカしてみましょう。今の回路ではバイアス電圧を単に電源電圧を抵抗分圧して得ているだけですから、アース側の10kΩに現れる電圧も「分圧比」に比例したものです。その比例関係を変えたいのです。

電源電圧上昇時にはバイアスが過大で、低下時には不足なのですから、この10kΩで分圧される電圧の何%かを固定してみようかと考えました。なお、100%固定にしますと・・・・?。3極管特性って能書きは、耳ざわりはイイかも知れませんけど、厄介でもある。

メモ的な表なので、分りにくくて当然の怪しからぬデーターです。ご容赦ください。

Ido=0.1Aを維持するバイアス電圧の中で、電源電圧変動に「適度」に対応する電圧分担を探るのに要した試行錯誤です。もっとスマートに・・・計算でも導き出せそうな気もするのですが、数学が苦手でして。

大雑把にはツェナダイオード、微調整にLEDやSiダイオードの順方向電圧で固定したわけです。

実は、この後の歪み率データーを残しておりません。試行錯誤途中の20111106時点での特性が、どうも気に食わぬ・・・2Wあたりからクロスオーバー歪が見える・・・とメモされてます。

これが、気に食わぬ特性。明らかに2W以上からのカーブが変わりました。コレ以降のバイアス回路いぢりでも、傾向が変わらぬ・・・ともメモされてまして、歪み率数値の安定性は良くなった・・・との書き残してます。なんか他人事みたい。

そろそろ実験に疲れて(飽きて)きました。昔なら中断・放置に至るパターンですが、なぜか「本番機」作製へと進みます。アタマが働かんのならてカラダを動かそうか、てな「逃避行動」かもしれません。

また開放構造?

20111120〜

前後左右が露出した「危険」な構造ですので、真似されると困ります。責任を追及されたらどうやって逃げようか。

拾い物のアルミパネル(約430×180mm)ありきの構造設計です。「超簡単・・・じゃ無くなったTRアンプ」類似構造の2作目です。箱に入れないで中身を晒す性癖が、潜在的にあるのかなあ。おお、コレ「30A5・SRPP」も同じか?。

レイアウト検討中の没ネタ。OPT以外の基幹部品は、殆ど役得JUNK。

パネル上の「お遊び」中でもあります。USソケット使ったところで、タマ風になるワケ無いのだが・・・。

3行空けのために・・・こげなことを

←この辺にパワーサーミスタ。KRT5D15MSFSCx2

3行空けのために・・・こげなことを

プチ難題(2)

20120121〜

本番機の出力段を組み込む段階で、新たに試したバイアス回路が、余計な問題を引き起こしてしまいました。

バイアス電圧の「半」固定部に、融通が利くと思ったTR回路を組みました。コンプリメンタリーSEPPでよく見るアレです。

出力デバイスへの熱結合はせず、の基板に置いたのですが、自己発熱?の接合部温度変化にも敏感。ON直後から生成電圧は減り、バイアスは「浅く」なってIdoがダラダラと微増・・・。またまた不毛な実験にハマった気分。

3行空けのために・・・こげなことを

次にやらかしたのが、コレ。1N4004の多数直列です。「半」固定電圧の全部ではありませんが、0.6V刻みのADJを目的として・・・それは出来ても、温度特性が絡み、TR式の二の舞です。凹みます。

どうやら「半」固定電圧は、ツェナダイオードだけで得たほうがマシな感じ・・・。

とはいえ、1V未満のADJをツェナだけで行うのも、なんだかな〜。1N4004x2を上限にして、既に得た適正バイアス電圧近似のツエナを新たに求めました。Vz≒6〜7V以上では若干「正」の温度特性を示すと聞きますが、ソコまでの細かい気配りをする心理的余裕がありません。

不思議な事に、V-FET素子そのものの温度特性には「厄介さ」を感じません。具体的には温度への依存性は少ない印象です。電源・バイアス電圧が安定していれば、Idの変化は見られず、ON後の1分未満で数%増える程度でした。だいたい整定した以後は、温度上昇中でもIdの増加は希少です。これは救われた気分。ただし、他のNEC・YAMAHA製品や、近年の「SIT」も同じかどうかは知りません。

結構な試行錯誤を経てたどり着いた、ACライン電圧対Ido変動の最終値。

AC電圧に対し、若干の「負」方向の電流変動を狙ったんですが、2対・4個のデバイスごとのADJは、もうこれ以上はご勘弁を・・・的なストレスでした。

ぼやき:プチ難題(1)(2)で費やした時間とエネルギーは、本件作製の半分?くらいの気分・・・。

本ページ最末尾に、後知恵策のメモ書き・・・2016年時点なので、遅すぎ!・・・。

完成間近だが

20120505〜

****

四つ角の「柱」を内装の設計変更に伴い、徐々にかさ上げしているのが見える写真です。中央部が撓むので、ゴム足も全6個に。

多数の端子台使用は、上下パネルの「完全」分離を目論み、出来た・・・はイイが、正直危なっかしい。事実、後に一度事故を起こしました。詳細は後述。

上パネルの後ろに電源・入出力の端子を置いたが、上下パネルの逆使いが正解だったと痛感。今更の話ですが。

3行空けのために・・・こげなことを

両ch出力段が完成してのラフテストでは、13Vrms/8Ω・・・約20W+20Wが3〜4%(1kHz)。電源部の10000μFx2間の5Ωは2.2Ωに変更したのですが、ココの出口は±40Vを割りそうな塩梅。

SRPP前段部の体裁も繕って、ラフテスト。単独詳細データを残せばよかったなあと。

全段込み、無帰還入出力特性です。左右利得差が1dbほどなのは普通?幸運?・・。各段共に局部帰還無し・・・とはいえませんが、殆ど丸裸同士のバディながら、上等と考えましょう。残りのデバイスで、最良バディを探す根気・気力が無いのです。

入力Volが20kΩ(A)なのを書き忘れてました。1μFでCUTしてるので・・・約8Hz。段間は、1μF・100kΩ(変更を書き忘れ)≒1.59Hz。つまりOPTの特性が結構関わってると思うが、これ以上の追求は放棄。

高域はOPT付きだが、案外良い・・・と、これも更なる追求は放棄。

3行空けのために・・・こげなことを

プチ難題(3)

20120521〜

先へ進む予定が、変な現象を見てしまいました。放置しておけんと判断。

SRPP前段込み。前段からのON電圧+変移が、結合コンデンサを介し出力段のバイアスに加算。Nchは増え、Pchは抑圧されている。出力段のみでは起きない現象。

これは対策後の、N/Pch各ソース電圧変移の様子。対策前は+0.7Aにも及んだが、+0.16Aに緩和。

対策は前段SRPPへの電源供給に、TR式のリプルフィルターを追加しただけ。電圧の立ち上がり遅延が目的です。全V-FETの看板は・・・微妙だ。

SRPP段への電源電圧は78Vほど。ハムも改善され、メデタシメデタシ。

3行空けのために・・・こげなことを

とにかく先へと

20120526〜

気になる事を見つけては時間食って、いささか焦ってます。

う〜ん・・・こんなに畝って大丈夫か?。実は、0.8Vrms/0.08W時の歪み率数値静定後、1分ほどの放置で0.024%→0.02%への低下を見つけました。どうもこれは測定レベル変更の都度起きる様子・・・。いやもう、見た上で放置。先へ行きます。

なお、仕上がり利得≒17db(7倍)です。

う〜ん、って。負帰還の効能が高域に偏ってる気もしますが、これならまあいいか。

3行空けのために・・・こげなことを

プチ難題(4)

20120603〜

良くないのです。定番の方形波応答で10kHzにオーバーシュート出てます。負荷開放で、発振します。あ〜あ、またか・・・。

コレもまた後の再現写真です。約800kHz・22Vp-p(7.7Vrms)。

OPT2次に、0.47μF+22Ωの積分補償で回避。その後、更に強化。また、その後に・・・・。

無帰還の段間・出力、各F特。スタガ比は無考慮でした。負荷開放時には出力段の利得が、ほぼ+10db増大したので、重ね合わせてみましたが・・・コレではもう・・・。

OPT付きとはいえ、タマ用のとは趣が違いますね。製品付属のグラフからも理解すべき点ですが、120Ω:16Ωちゅうのは広帯域ですな。いや、TANGOだからなのか。

2次補償の効きを見たつもりが、なんだか意味を成さない感じではある。

それと、なんだか高域パワーが食われている気分。いや、事実食ってるんですが。

これも無駄な検査データ?。いや、ココから有用な処方を導き出せない「ヤブ」なのかもしれません。

右のも10Ω+1μFカマしてるはずだが、実験ノートに明記なし。

10db内外の負帰還で、ここまで高域が伸びるとは予想外。

一番派手な波形がコレ。開放0.022μFと0.047μFの純容量負荷時。

2次補償を10Ω+1μFに強化してもこれだもの。

いらぬ誤解をしていたようです。幾つかの文献・・・ぶっちゃけると武末先生のですが・・・で、負帰還抵抗に並列する「高域微分補償」は容量負荷に弱い云々。その事もあって試しておりませんでしたが、ソレ(初っ端から1000pF)をやりましてホドホドに治まりました。

最終回路・特性

20120616〜

もう、なにも起きないで・・・と祈るような気持ちで得た特性です。2次補償は0.22μF+10Ωに緩和しました。

入出力特性測定はサボリましたが、約11dbの負帰還で仕上がり利得約17dbです。Noisは0.1m〜0.2mV内外(500kHz・BW測定)で、Lchは良好。

初段の下側ソース抵抗値ADJで“2次歪み打ち消し”を目論みましたが、これまでの経緯から精密な追い込みは「無駄」と判断しました。SRPP上下の電圧が極端に違わない範囲で、「テキトー」な歪み低下が見える程度に留めてます。

これらは注入法で得ました。それにしても案外「内部抵抗」は高いんですね。

これらは注入法で得ました。それにしても案外「内部抵抗」は高いんですね。

粗い計算でも、片素子のrd≒60Ω?・・・深いバイアスやら、1Ωのソース抵抗も絡んでる気はしますが、検証する気が起きませぬ。

いままで滅多に調べた事が無い「chセパレーション」。電源回路がアレなので調べたらコレですもん、当たり前か。なお、0db=10Vrmsは過酷でした。

いままで滅多に調べた事が無い「chセパレーション」。電源回路がアレなので調べたらコレですもん、当たり前か。なお、0db=10Vrmsは過酷でした。

標準PPと同一動作の出力段・・・と考えていましたが、電源に対してはシングル動作と変わりないようです。信号電流経路に電源部が含まれるワケだ。

一番派手だったのは、処置後の今でも一番です。0.022μFと0.047μFの純容量負荷時。

入力波形を示す下にもリンギング・・・いささか胡散臭い。

3行空けのために・・・こげなことを

永らく「載せ忘れてた」最終回路。実は・・・20141022時点で「現物」を探りながら書いたのです。

古いExcelとPaintに頼った描画の都合か、はたまた自身のスキル不足か・・・両方か、2分割にならざるを得ない。

入力端子は2種設置。左図下側は出力段への“お遊び的”ダイレクト入力です。16Ωタップへの8Ω負荷までの利得は+1db弱でして、CD機のH/P出力(負荷開放時、約5Vrms/0dbFS)を繋ごうと企てました。その際は、前段2SK79ユニットを引き抜くのです。ただし、ソレを試した事が無く、「能書き」に過ぎませんな。

まとめ

201206**〜

途中から「最適化」を放棄した流れになりました。もう「カタチ」を作り上げる事が第一で、放置ネタにしたくないだけ。死蔵のままかも知れん部品を、無理やりハメ込んだ態です。

濃くて太い音と聞いた。細かい事(音?)はどーでもイイ、てな鳴りっぷりは案外爽快。

作って調べた本人の感覚だが、低域のchセパレーション悪化を知ってるので、関連性をコジツケたくもある。左右の妙な歪み差は・・・聞いてて解りませんなあ。

あちこちに橙色LEDでライトアップ・・・もう、コレきりでやめる。

ボヤキ(1):製作中のチョンボで片chのK60だったかのバイアスを失った事があり、ソースの1Ω焼損でデバイスの昇天は回避できたが結果論かも。デバイスの予備は両ch分ありますが、バイアスがらみのADJは覚悟せねばなりません。ツェナ電圧の微調(交換ですがな)を要さないで済むことを祈るしかない。

ボヤキ(2):後日J18/K60の検索をしますと、若松では消えてた。見知らぬ店の、J/K共@2835円くらいか。まあ・・・また何処からか湧いて出てくる気もするが、MOSデバイスへの代替も考慮した方が良さそうですな。V-FET云々の看板は降ろすしかないけれど。なお、2SK79ペアは若松の扱いが継続。以上20140915時点。

地元、自作オーディオ発表会出品

20141109

オーディオ音楽クラブ名古屋、第11回発表会に出品。前回は「30MP27・OTL」が小出力のため、ヒヤヒヤものでしたが、今回は安心でした。

右、テーブル上の本機。直前に入手した「ポップアップ・バッグ」にピッタリ納まり、ボロ隠ししております。左は同日参加者様の作品、GM70シングルや40KG6A・OTLなど、力作ぞろい。そんな中で、荒っぽい拵え方の本機は異質だったかも。

今回は、左端に見え隠れしているタンノイSPをお借りしました。90db前半?の能率かと存じますが、充分”煩く”鳴って良かった。

荒っぽい出品作に合わせて?、持参したCDも“荒っぽい”気がしました。R&B系の楽曲など流す方はおられません。

荒っぽい出品作に合わせて?、持参したCDも“荒っぽい”気がしました。R&B系の楽曲など流す方はおられません。

試聴者の中(お名前を失念しており、申し訳ございません)に、エリック・バードン&ウォーをご存知の方がいらっしゃいました。それだけで単純に嬉しいのです。

20160517時点の後知恵ネタ・・・「半」固定バイアス電圧の生成に、シャント・レギュレータ素子「TL-431」などが良さそうなどと思いつく。ただし、組み換えを実施する気は・・・まだ起きない。